# HANDBOOK OF THIN-FILM DEPOSITION PROCESSES AND TECHNIQUES

# Principles, Methods, Equipment and Applications

### **Second Edition**

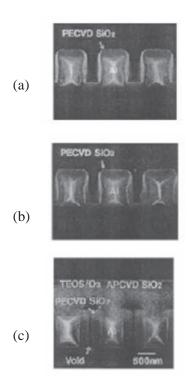

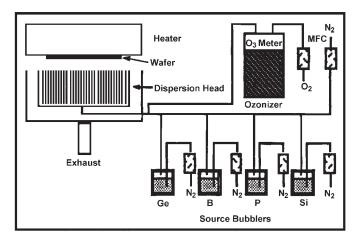

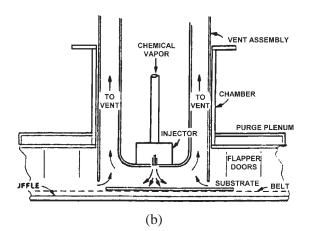

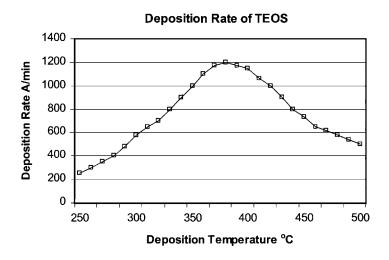

Edited by

### Krishna Seshan

Intel Corporation Santa Clara, California

NOYES PUBLICATIONS WILLIAM ANDREW PUBLISHING Norwich, New York, U.S.A. Copyright © 2002 by Noyes Publications No part of this book may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission in writing from the Publisher.

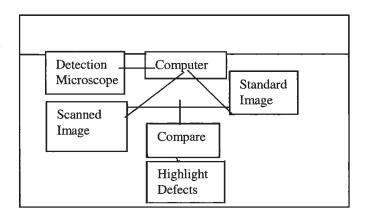

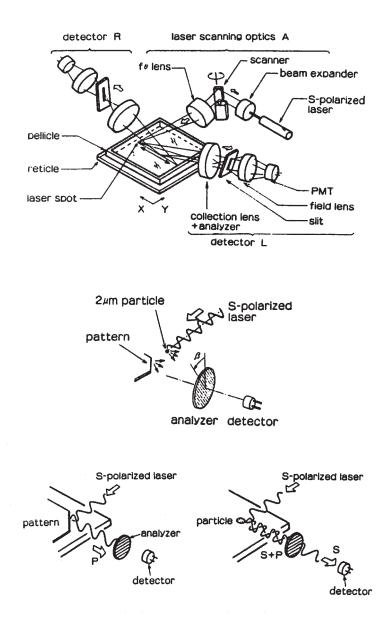

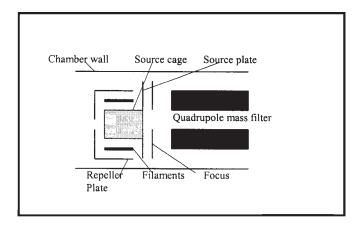

Library of Congress Catalog Card Number: 2001135178 ISBN: 0-8155-1442-5 Printed in the United States

Published in the United States of America by Noyes Publications / William Andrew Publishing 13 Eaton Avenue Norwich, NY 13815 1-800-932-7045 www.williamandrew.com www.knovel.com

10 9 8 7 6 5 4 3 2 1

Library of Congress Cataloging-in-Publication Data

Handbook of Thin-Film Deposition Processes and Techniques / [edited] by Krishna Seshan. -- 2nd edition p. cm. Includes bibliographical references and index. ISBN 0-8155-1442-5 1. Thin film devices -- Design and construction -- Handbooks, manuals, etc. I. Seshan, Krishna. II. Title. TK7872.T55H36 2001135178 621.381'72--dc19 CIP

#### NOTICE

To the best of our knowledge the information in this publication is accurate; however the Publisher does not assume any responsibility or liability for the accuracy or completeness of, or consequences arising from, such information. This book is intended for informational purposes only. Mention of trade names or commercial products does not constitute endorsement or recommendation for use by the Publisher. Final determination of the suitability of any information or product for use contemplated by any user, and the manner of that use, is the sole responsibility of the user. We recommend that anyone intending to rely on any recommendation of materials or procedures mentioned in this publication should satisfy himself as to such suitability, and that he can meet all applicable safety and health standards.

#### MATERIALS SCIENCE AND PROCESS TECHNOLOGY SERIES

#### Series Editors

Gary E. McGuire, Microelectronics Center of North Carolina

Stephen M. Rossnagel, IBM Thomas J. Watson Research Center

Rointan F. Bunshah, University of California, Los Angeles (1927–1999), founding editor

#### **Electronic Materials and Process Technology**

CHARACTERIZATION OF SEMICONDUCTOR MATERIALS, Volume 1: edited by Gary E. McGuire

CHEMICAL VAPOR DEPOSITION FOR MICROELECTRONICS: by Arthur Sherman

CHEMICAL VAPOR DEPOSITION OF TUNGSTEN AND TUNGSTEN SILICIDES: by John E. J. Schmitz

CHEMISTRY OF SUPERCONDUCTOR MATERIALS: edited by Terrell A. Vanderah CONTACTS TO SEMICONDUCTORS: edited by Leonard J. Brillson

DIAMOND CHEMICAL VAPOR DEPOSITION: by Huimin Liu and David S. Dandy

DIAMOND FILMS AND COATINGS: edited by Robert F. Davis

DIFFUSION PHENOMENA IN THIN FILMS AND MICROELECTRONIC MATERIALS: edited by Devendra Gupta and Paul S. Ho

ELECTROCHEMISTRY OF SEMICONDUCTORS AND ELECTRONICS: edited by John McHardy and Frank Ludwig

ELECTRODEPOSITION: by Jack W. Dini

HANDBOOK OF CARBON, GRAPHITE, DIAMONDS AND FULLERENES: by Hugh O. Pierson

HANDBOOK OF CHEMICAL VAPOR DEPOSITION, Second Edition: by Hugh O. Pierson HANDBOOK OF COMPOUND SEMICONDUCTORS: edited by Paul H. Holloway and Gary E. McGuire

HANDBOOK OF CONTAMINATION CONTROL IN MICROELECTRONICS: edited by Donald L. Tolliver

HANDBOOK OF DEPOSITION TECHNOLOGIES FOR FILMS AND COATINGS, Second Edition: edited by Rointan F. Bunshah

HANDBOOK OF HARD COATINGS: edited by Rointan F. Bunshah

HANDBOOK OF ION BEAM PROCESSING TECHNOLOGY: edited by Jerome J. Cuomo, Stephen M. Rossnagel, and Harold R. Kaufman

HANDBOOK OF MAGNETO-OPTICAL DATA RECORDING: edited by Terry McDaniel and Randall H. Victora

HANDBOOK OF MULTILEVEL METALLIZATION FOR INTEGRATED CIRCUITS: edited by Syd R. Wilson, Clarence J. Tracy, and John L. Freeman, Jr.

HANDBOOK OF PLASMA PROCESSING TECHNOLOGY: edited by Stephen M. Rossnagel, Jerome J. Cuomo, and William D. Westwood

HANDBOOK OF POLYMER COATINGS FOR ELECTRONICS, *Second Edition:* by James Licari and Laura A. Hughes

HANDBOOK OF REFRACTORY CARBIDES AND NITRIDES: by Hugh O. Pierson

HANDBOOK OF SEMICONDUCTOR SILICON TECHNOLOGY: edited by William C. O'Mara, Robert B. Herring, and Lee P. Hunt

#### vi Series

HANDBOOK OF SEMICONDUCTOR WAFER CLEANING TECHNOLOGY: edited by Werner Kern

HANDBOOK OF SPUTTER DEPOSITION TECHNOLOGY: by Kiyotaka Wasa and Shigeru Hayakawa

HANDBOOK OF THIN FILM DEPOSITION PROCESSES AND TECHNIQUES, Second Edition: edited by Krishna Seshan

HANDBOOK OF VACUUM ARC SCIENCE AND TECHNOLOGY: edited by Raymond L. Boxman, Philip J. Martin, and David M. Sanders

HANDBOOK OF VLSI MICROLITHOGRAPHY, *Second Edition:* edited by John N. Helbert HIGH DENSITY PLASMA SOURCES: edited by Oleg A. Popov

HYBRID MICROCIRCUIT TECHNOLOGY HANDBOOK, Second Edition: by James J. Licari and Leonard R. Enlow

IONIZED-CLUSTER BEAM DEPOSITION AND EPITAXY: by Toshinori Takagi

MOLECULAR BEAM EPITAXY: edited by Robin F. C. Farrow

NANOSTRUCTURED MATERIALS: edited by Carl. C. Koch

SEMICONDUCTOR MATERIALS AND PROCESS TECHNOLOGY HANDBOOK: edited by Gary E. McGuire

ULTRA-FINE PARTICLES: edited by Chikara Hayashi, R. Ueda and A. Tasaki

WIDE BANDGAP SEMICONDUCTORS: edited by Stephen J. Pearton

#### **Related Titles**

ADVANCED CERAMIC PROCESSING AND TECHNOLOGY, Volume 1:edited by Jon G. P. Binner

CEMENTED TUNGSTEN CARBIDES: by Gopal S. Upadhyaya

CERAMIC CUTTING TOOLS: edited by E. Dow Whitney

CERAMIC FILMS AND COATINGS: edited by John B. Wachtman and Richard A. Haber CORROSION OF GLASS, CERAMICS AND CERAMIC SUPERCONDUCTORS: edited by David E. Clark and Bruce K. Zoitos

FIBER REINFORCED CERAMIC COMPOSITES: edited by K. S. Mazdiyasni

FRICTION AND WEAR TRANSITIONS OF MATERIALS: by Peter J. Blau

HANDBOOK OF CERAMIC GRINDING AND POLISHING: edited by Ioan D. Marinescu, Hans K. Tonshoff, and Ichiro Inasaki

HANDBOOK OF HYDROTHERMAL TECHNOLOGY: edited by K. Byrappa and Masahiro Yoshimura

HANDBOOK OF INDUSTRIAL REFRACTORIES TECHNOLOGY: by Stephen C. Carniglia and Gordon L. Barna

$\label{eq:mechanical alloying for FABRICATION OF ADVANCED ENGINEERING MATERIALS: by M. Sherif EI-Eskandarany$

SHOCK WAVES FOR INDUSTRIAL APPLICATIONS: edited by Lawrence E. Murr SOL-GEL TECHNOLOGY FOR THIN FILMS, FIBERS, PREFORMS, ELECTRONICS AND SPECIALTY SHAPES: edited by Lisa C. Klein

SOL-GEL SILICA: by Larry L. Hench

SPECIAL MELTING AND PROCESSING TECHNOLOGIES: edited by G.K. Bhat SUPERCRITICAL FLUID CLEANING: edited by John McHardy and Samuel P. Sawan Dedications

To the memory of George Narita (1928–2001): kind, patient, wise, nurturing editor, and good friend.

> To the memory of my beloved parents, Kalpakam and P. K. Seshan.

### Contributors

**Suresh Bhat** Intel Corporation, Santa Clara, CA

Kenneth C. Cadien Intel Corporation Hillsboro, OR

**Robert Chow** Thin Film Division Varian Associates Santa Clara, CA

**George J. Collins** Department of Electrical Engineering Colorado State University Fort Collins, CO

**Cheri Dennison** KLA-Tencor Corporation Milpitas, CA

John Foggiato Quester Technology, Inc. Fremont, CA Martin L. Hammond Tetron/Gemini Systems Fremont, CA

Mark Keefer KLA-Tencor Corporation Milpitas, CA

Werner Kern David Sarnoff Research Center RCA Laboratories Princeton, NJ

Walter S. Knodle High Yield Technology, Inc. Mountain View, CA

James J. McNally Air Force Academy Colorado Springs, CO

John R. McNeil Department of Electrical Engineering University of New Mexico Albuquerque, NM **Cameron A. Moore** Department of Electrical Engineering Colorado State University Fort Collins, CO

**Rebecca Pinto** KLA-Tencor Corporation Milpitas, CA

**Paul D. Reader** Ion Tech, Inc. Fort Collins, CO

**Stephen Rossnagel** IBM Research Division Yorktown Heights, NY

**Laura B. Rothman** IBM Yorktown Heights, NY

**Dominic J. Schepis** IBM East Fishkill, NY

**Klaus K. Schuegraf** Tylan Corporation Carson, CA **Krishna Seshan** Intel Corporation Santa Clara, CA

Vivek Singh Intel Corporation Hillsboro, OR

Lance R. Thompson Sandia National Labs Albuquerque, NM

James Turlo KLA-Tencor Corporation Milpitas, CA

**Zeng-qi Yu** Colorado State University Fort Collins, CO

John L. Zilko Optoelectrics Division Agere Systems Breinigsville, PA

### Foreword

### Gordon E. Moore

Increasingly any references to the current technology for the manufacture of integrated circuits as "semiconductor technology" is a misnomer. By now the processing relating to the silicon itself contributes relatively few steps to the total while the various processes associated with the deposition and patterning of the increasing number of metal and insulating films have grown in importance. Where the first metal-oxidetransistor circuits of the 1960's took five masking steps to complete, and even early silicon-gate circuits with single metal layer interconnections took only seven, modern circuits with as many as six layers of metal take well in excess of twenty. Not only are there more layers, but the composition of those layers is often complex. Metal conduction layers might require barrier films to prevent inter-diffusion or to enhance adhesion. Insulators not only isolate circuit elements electrically, but are used to prevent ions from harming the electrical properties of the transistors. In fact, if the technology for integrated circuit manufacture as practiced today were named for the majority of the processing steps, the technology could probably be more accurately described as *thin-film technology*.

Consistent with this change, the processing for the deposition and patterning of films has received major research and engineering emphasis and has evolved rapidly over the last few decades. Where in the '60's, thermal oxidation or vapor deposition was sufficient for the insulators and evaporation or sputtering of aluminum took care of the needs for conductors, a large variety of sophisticated deposition techniques have grown with the industry. Today one can control both the electrical and mechanical properties while achieving uniform and reproducible films from a few atomic layers thick to several micrometers. The chemistry and physics of the films are becoming increasingly better understood, but as they are, the demands of the device designer become more stringent. For example, where the dielectric constant of silicon oxide-based insulators was accepted as a design parameter to live with for thirty years or so, capacitance associated with interconnections now can be a real limitation on circuit performance. Designers want an insulator with all the good properties they have come to love with SiO<sub>2</sub>, but with a dielectric constant as close to that of a vacuum as possible. Similarly, with conductors no one will be happy until we have room temperature super-conducting films in multi-layered structures.

The simple furnaces and evaporators of yesteryear have become multi-chamber creations of stainless steel that allow a series of processes to be done without exposing the work to air. The lithography machines for creating the desired precise and fine-scaled patterns now cost several million dollars each as the industry pushes the limits of optical systems in the continuing pursuit of performance and small size. The cumulative investment in developing and improving processes must exceed a hundred billion dollars by now. Such a huge investment of money and technical talent has created a vast amount of knowledge, much of which is summarized in this volume.

The film technology developed primarily for the silicon integrated circuit industry is finding its way into several other areas of application. It has become a general technology for designing and constructing complex structures, layer-by-layer. Micro-electromechanical devices (MEMs) use the same deposition and patterning techniques. Micro-fluidic gadgets with micro-sized pipes, valves and all the plumbing necessary to make tiny chemical factories or analytical laboratories are increasingly important, and again use the film technologies that grew up around semiconductor integrated circuits. Even the gene chips the biotech industry uses to speed up their analysis come from the same bag of tricks.

This book takes a snapshot of the state of the art in various technologies relating to thin films. It brings together in one convenient location a collection of the research results that have been gathered by many groups over the last few decades. It will be something that the concerned engineer will return to time after time in the course of his or her work. This is the forefront of science and process engineering with important bearing on many modern industries.

## **Recent Changes in the Semiconductor Industry**

Krishna Seshan

The size, importance, and the economic impact of the semiconductor industry have undergone a sea change in recent years. The role of equipment has been the fuel for this change. New processing steps have become necessary, old ones have become cleaner, greener and more sophisticated. Everything has become much cleaner and more expensive; it is common for pieces of equipment to cost multiple millions of dollars. The result is a new manufacturing environment for the industry.

#### **1.0 COST OF DEVICE FABRICATION**

Graphs and tables in this section quantify that semiconductor fabricators generate large revenues, but their manufacturing costs have also become very large. This increase in equipment cost is driven by the need for very clean fabricators and processing steps. The connections between feature size, contamination control, and cost are discussed below.

#### 2 Thin-Film Deposition Processes and Technologies

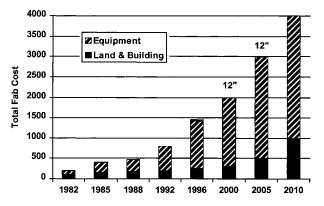

The graph in Fig. 1 shows a breakdown of the cost of device fabrication into equipment and land/building costs. It is clear that the equipment component of cost is now the major contributor. Notice the increase as the industry moves to 12" wafers.

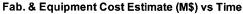

The growth of the semiconductor industry and the sales of processing equipment are related as shown in Fig. 2.

Figure 1. Equipment component of total fabrication costs is increasing much faster than land and buildings. (*Source: Dataquest Report 2000.*)

**Figure 2.** Electronic equipment sales, semiconductor sales value, and yearly fluctuations. (*Data adapted from "Worldwide IC Industry Economic Update and Forecast."*)

The graphs above make the following three points:

- Costs of device fabrication have increased. The cost of a 12" fab is in the billions of dollars.

- The value of the semiconductor products manufactured, memory and mircroprocessors, is measured in the billions of dollars.

- A large fraction of the fabricator's cost is the cost of manufacturing equipment. This book is a detailed account of the processes performed by the equipment.

#### 1.1 Role of Cleanliness in Cost of Equipment

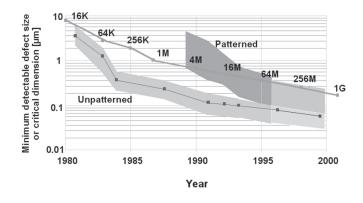

By far the biggest change has been our understanding of the role of defects and particle sizes as the lithography moves into the nanometer regime. Table 1 shows industry estimates of defect densities that can be tolerated. It is implied that the defects at or smaller than the litho size can be fatal, causing yield loss.

The table also shows how the mask layers increase and the number of defects per unit area have to decrease. This table emphasizes the importance of cleanliness in semiconductor processing. It is for this reason that a new chapter on contamination and contamination control (Ch. 7) has been added to this edition.

| Year                                               | 1999 | 2001 | 2003 | 2006 | 2009 |

|----------------------------------------------------|------|------|------|------|------|

| Technology Generation (nm)                         | 180  | 150  | 130  | 100  | 70   |

| Mask Count                                         | 22   | 24   | 24   | 26   | 28   |

| Allowable Defect per sq.<br>meter to get 60% yield | 78   | 60   | 55   | 43   | 34   |

**Table 1.** Projected Increase in Mask Layers and Decrease in Allowable

Defects

#### 1.2 Role of Chip Size Trends, Larger Fabricators, and 12" Wafers

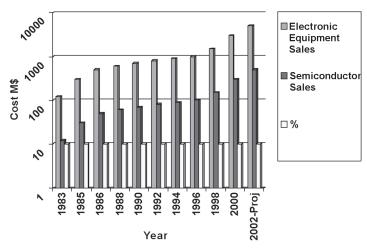

The importance of clean fabrication facilities and equipment becomes all the more pertinent when we consider that chip sizes with increased functionality increase with time and with decreasing lithography feature size. This is shown in the graph below (Fig. 3).

As chip size increases, so does the need for more wafer starts. One direction the industry has to go is to move the fabricators to larger size wafers.

Figure 3. Plot of chip size in mm<sup>2</sup> vs. lithographic generation. These are best guess estimates. The point to note is that die that can be expected fill the litho field size (800 mm  $\times$  800 mm).

### **1.3** Lithography, Feature Size, and Cleaner Fabricators and Equipment

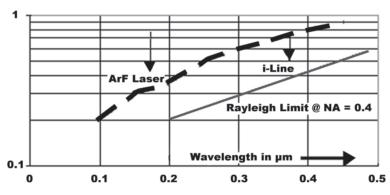

There are two connected variables that one needs to understand. The number of critical mask layers increase; a critical layer is one where high degree of registration and small widths are required. In these layers, defects at the resolution limit can become critical. An example is metal debris shorting two metal lines. The graph in Fig. 4 shows the dimensions that are involved.

**Figure 4.** This graph of printable line width estimate vs litho wavelength shows that particles as small as 250 nm could become critical defects. As line width decreases, more layers become critical, and cleaner the tool and the fabricators have to become.

#### 1.4 Defect Density and the Need for Cleaner Fabricators

There are two complications with defect density. First, the mask count is increasing and the number of critical layers is increasing. Mask layers are expected to increase from 20 mask layer levels to 30. Secondly, the line size is decreasing—so smaller defects become killer defects. The net result is that both fabricators and equipment has to become cleaner. One way to measure this is to track what the critical defect density,  $D_0$  (defects/m<sup>2</sup>), needs to be to get 60% yield as shown in Table 2. These numbers are based on predicted chip size areas and are shown here in order to explain the trend. These are not exact numbers.

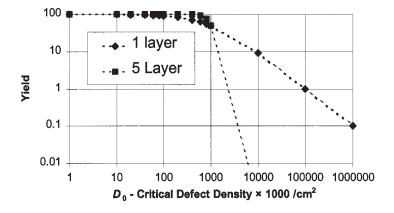

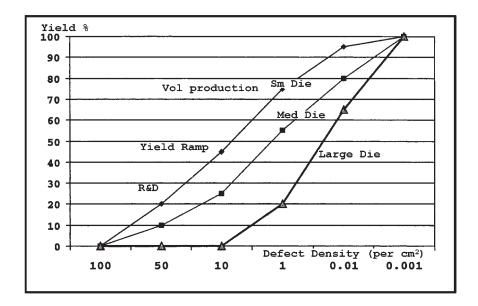

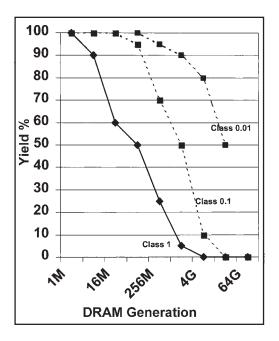

The need for decreased feature sizes and the increase in the number of critical masking layers drive cleaner fabricators. It is instructive to examine the plot of cumulative yield vs the critical defect concentration as shown in Fig. 5. This graph shows that a defect density of 0.5/cm<sup>2</sup> will reduce the yield by about 1%. It is evident from the graph that both fabricators and equipment will have to meet stringent cleanliness standards, at least Class 10 or better. Class 10 clean rooms are expensive to build—with estimates of thousands of dollars per sq. foot.

Cleanroom Class designations generally refer to the Federally agreed-upon standards set forth in FED STD 209B which is shown in part in Table 3.<sup>[1]</sup>

|                                             | 1999 | 2001 | 2003 | 2006 |

|---------------------------------------------|------|------|------|------|

| Generation                                  | 250  | 180  | 150  | 130  |

| DRAM <i>D</i> <sub>0</sub> for<br>60% yield | 1400 | 1000 | 850  | 700  |

| Logic $D_0$ for 60% yield                   | 1400 | 1200 | 1000 | 900  |

**Table 2.** Estimates of  $D_0$ , the Critical Defect Density Required

**Figure 5.** The yield equation is plotted for a one and a five critical-layer process. Notice that to get 60% yeild, the equipment and fabricators have to be better than a defect level of 0.01-0.03 defects/cm<sup>2</sup>.

| Table | 3. Specifications | From | FED | STD 2 | 209B |

|-------|-------------------|------|-----|-------|------|

|-------|-------------------|------|-----|-------|------|

| Class   | Particles/liter<br>0.5 µm and larger | Particles<br>5 µm and larger |

|---------|--------------------------------------|------------------------------|

| 100     | 3.5                                  |                              |

| 1000    | 35                                   |                              |

| 10,000  | 350                                  | 65                           |

| 100,000 | 3500                                 | 700                          |

#### 1.5 Conclusions

The preceding brief discussion and data shows the following:

- Improved lithography decreases feature size.

- The number of mask layers increase because of higher integration of chip design.

- These combine to call for smaller defects and cleaner processing conditions.

- Equipment then has to become more sophisticated, cleaner, and more expensive.

### 2.0 TECHNOLOGY TRENDS, CHIP SIZE, PERFORMANCE, AND MOORE'S LAW

The semiconductor industry follows a predictable trend—one where the transistor density doubles every generation, in about 3-year cycles. This has come to be known as Moore's Law. In the section below, these trends are examined in detail

In order to simplify and unify the growth predictions of the industry, the SIA (Semiconductor Industry Association) publishes a roadmap, the SIA Industry Roadmap. The numbers shown in Table 4 are drawn from that report.<sup>[1]</sup>

|                                   |      |      |      | -    |      | -    |      |

|-----------------------------------|------|------|------|------|------|------|------|

| Year of<br>Shipment               | 1997 | 1999 | 2001 | 2003 | 2006 | 2009 | 2012 |

| DRAM<br>Half<br>Pitch(nm)         | 250  | 180  | 150  | 130  | 100  | 70   | 50   |

| Memory<br>(sample)                | 256M | 1G   |      | 4G   | 16G  | 64G  | 256G |

| Memory<br>(ship)                  | 64M  | 256M | 1G   | 1G   | 4G   | 16G  | 64G  |

| Bits/cm <sup>2</sup><br>at sample | 96M  | 270M | 380M | 770M | 2.2B | 6.1B | 17B  |

| Logic<br>Txtor/cm <sup>2</sup>    | 3.7M | 6.2M | 10M  | 18M  | 39M  | 84M  | 180M |

Table 4. SIA Industry Roadmap<sup>[1]</sup>

#### 8 Thin-Film Deposition Processes and Technologies

DRAM devices are historically viewed as technology drivers. Now microprocessors have closed the technology gap. DRAM focus is on minimization of area occupied by memory cells. To increase cell density the cell size must be as small as possible. In microprocessors, performance is dominated by the length of the transistor gate and by the number of interconnect layers.

#### 2.1 Performance of Packaged Chips—Trends

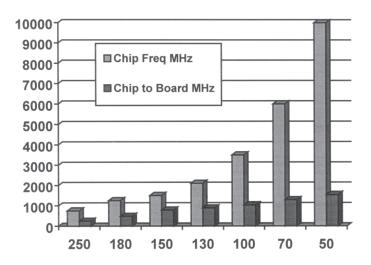

Performance increase follows the decrease in cell size: the transistor drives increase and switching times decrease because the charge being switched decreases. This enables larger chips to be designed and more functionality to be integrated. These trends may be seen in the Fig. 6

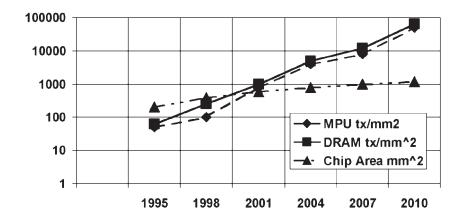

An empirical observation made by Gordon Moore can be seen in Fig. 7. Often chip size, or the number of transistors, or the density is plotted. All three graphs show the same trend: one that says that density doubles every generation or about three years.

Figure 6. As cell sizes decrease, the chip frequencies increase.

**Figure 7.** Projected growth of DRAMs and MPUs. The chip sizes are also plotted. Microporcessor density tends to be lower than DRAM density because logic circuits cannot be drawn as tightly as memory.

#### REFERENCES

- 1. *National Technology Roadmap for Semiconductors*—SIA (1997). The most recent roadmap should be consulted for exact figures. Most of the data used in this chapters are drawn from this book only to show the trends.

- Mittal, K. L. (editor), *Treatise on Clean Surface Technology*, Vol. 1, Plenum, New York (1987)

- 3. IC Technology Trends, ICE Corp. (2001)

- Rubloff, G. W., and Bordonaro, D. T., Manufacturing Trends, *IBM J. Res.* and Dev., 36(2) (March, 1992)

### **Preface to the Second Edition**

This book is the second edition of the popular book on thin-film deposition by Klaus K. Schuegraf. The previous edition is more than twelve years old. While the fundamentals have not changed, the industry has grown enormously. We've included an introductory chapter, "Recent Changes in the Semiconductor Industry," which describes these changes. In addition, many new manufacturing processes, like chemical mechanical polishing (CMP), have become mature. These are among the many factors that necessitated this new edition.

After the introductory chapter, this second edition starts with the "Introduction and Overview," Ch. 1 from the first edition written by W. Kern and K. Schuegraf. This chapter contains fundamentals that have not changed.

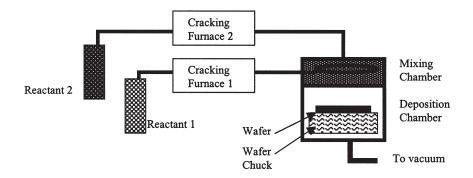

While the methods of growing epitaxial silicon have become much more sophisticated, the fundamentals are still the same and this is reflected by our inclusion of the original chapter on "Silicon Epitaxy by Chemical Vapor Deposition" by M. L. Hammond.

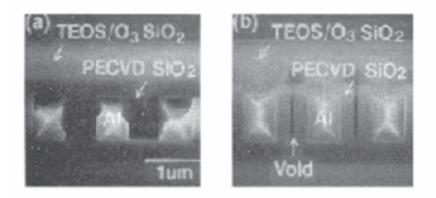

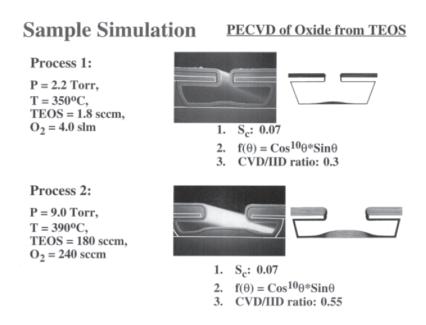

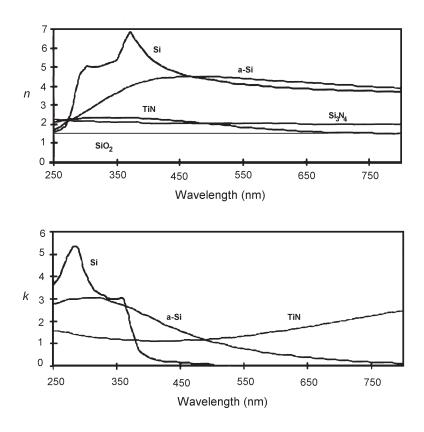

Chapter 3 on "Chemical Vapor Deposition of Silicon Dioxide Films" by J. Foggiato covers some new aspects of atmospheric and low pressure CVD oxide deposition methods.

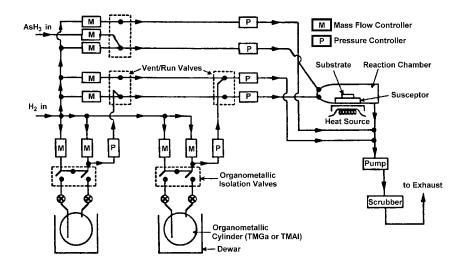

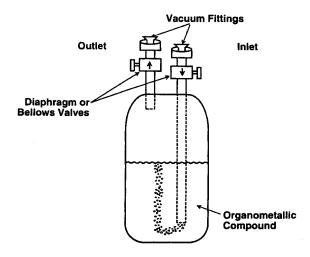

Chapter 4 on "Metal Organic CVD" by J. L. Zilko has been updated with new material. These four chapters constitute the first part of the book.

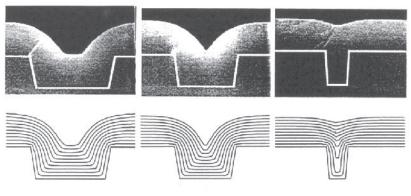

A completely new chapter on "Feature Scale Modeling" by V. Singh helps make the transition to physical deposition methods. Modeling of deposition processes has become mature, improving our ability to define design rules for metal height and spacing to avoid porosity and pinholes that later compromise reliability.

Going hand-in-hand with modeling is our ability to measure both thickness and spacing of submicron dimensions. This has led to the growth of many automatic and sophisticated metrology tools, and the fundamentals behind these instruments is described in the new chapter on the "Role of Metrology and Inspection" by M. Keefer, et al.

New metrology methods are also the backbone of "Contamination Control, Defect Detection and Yield Enhancement" by S. Bhat and K. Seshan, Ch. 7. The understanding of the connection between lithography and contamination has become much more quantitative and this new chapter deals with this subject.

A new chapter on "Sputtering and Sputter Deposition" by S. Rossnagel and three chapters from the first edition bring together all the Physical Vapor Deposition methods. The chapters from the first edition include Ch. 9, "Laser and E-beam Assisted Processing," by C. Moore, et al., Ch. 10 on "Molecular Beam Epitaxy" by W. S. Knodle and R. Chow, and Ch. 11, "Ion Beam Deposition," by J. R. McNeil, et al. These methods remain central to many metal interconnect technologies.

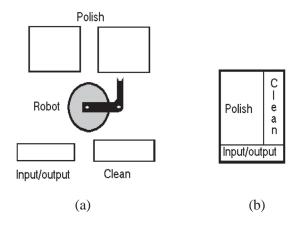

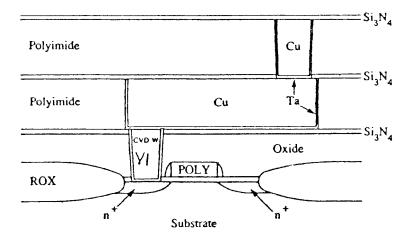

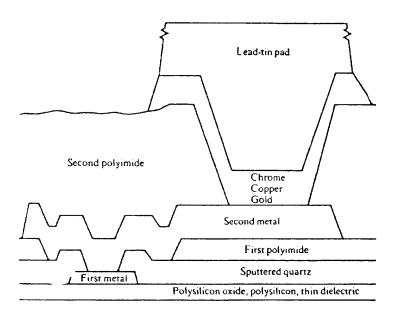

Chapters 12 and 13 are devoted to two entirely new areas. Chapter 12, "Chemical Mechanical Polishing" by K. Cadien, deals with this method of attaining the flatness that is required by modern lithography methods. This technique is so central that several—if not all—layers are polished. Chapter 13, written by K. Seshan, et al., describes new materials that are used for interconnect dielectric materials—specifically organic polyimide materials.

Chapter 14, "Performance, Processing, and Lithography Trends" by K. Seshan, contains a summary of the book and a peek into the future.

The audience for this handbook is the practicing engineer in the microelectronics industry. It will also be useful for engineers in related industries like the magnetic memory, thin film displays, and optical interconnect industries. These industries use many of the same processes, equipment, and analysis techniques. The book could also be used as a supplement to graduate courses in semiconductor manufacturing.

San Jose, California August, 2001 Krishna Seshan

### **Preface to the First Edition**

The technology of thin film deposition has advanced dramatically during the past 30 years. This advancement was driven primarily by the need for new products and devices in the electronics and optical industries. The rapid progress in solid-state electronic devices would not have been possible without the development of new thin film deposition processes, improved film characteristics and superior film qualities. Thin film deposition technology is still undergoing rapid changes which will lead to even more complex and advanced electronic devices in the future. The economic impact of this technology can best be characterized by the worldwide sales of semiconductor devices, which exceeded \$40 billion in 1987.

This book is intended to serve as a handbook and guide for the practitioner in the field, as a review and overview of this rapidly evolving technology for the engineer and scientist, and as an introduction for the student in several branches of science and engineering.

This handbook is a review of 13 different deposition technologies, each authored by experts in their particular field. It gives a concise reference and description of the processes, methods, and equipment for the deposition of technologically important materials. Emphasis is placed on recently developed film deposition processes for application in advanced microelectronic device fabrications that require the most demanding approaches. The discussions of the principles of operation for the deposition equipment and its suitability, performance, controls, capabilities and limitations for production applications are intended to provide the reader with basic understanding and appreciation of these systems. Key properties and areas of application of industrially important materials created by thin film deposition processes are described. Extensive use of references, reviews and bibliographies provides source material for specific use and more detailed study.

The topics covered in each chapter of this book have been carefully selected to include advanced and emerging deposition technologies with potential for manufacturing applications. An attempt was made to compare competing technologies and to project a scenario for the most likely future developments. Several other deposition technologies have been excluded since adequate recent reviews are already available. In addition, the technology for deposition or coating of films exceeding 10 microns in thickness was excluded, since these films have different applications and are in general based on quite different deposition techniques.

Many people contributed and assisted in the preparation of this handbook. My thanks go to the individual authors and their employers, who provided detailed work and support. I am especially indebted to Werner Kern, who provided many valuable suggestions and assisted in co-authoring several sections of this book. Last but not least, my special thanks go to George Narita, Executive Editor of Noyes Publications, for providing continued encouragement and patience for the completion of all the tasks involved.

Torrance, California July, 1988 Klaus K. Schuegraf

# Contents

| Foreword by    | Gordon E. M  | looreix                                  |

|----------------|--------------|------------------------------------------|

| Preface to the | Second Edi   | tionxi                                   |

| Preface to the | First Editio | nxiii                                    |

| Contributors   |              |                                          |

| Recent Cha     | nges in the  | Semiconductor Industry1                  |

| Krishn         | Seshan       |                                          |

| 1.0            | COST OF I    | DEVICE FABRICATION1                      |

|                | 1.1 Role     | of Cleanliness in Cost of Equipment3     |

|                | 1.2 Role     | of Chip Size Trends, Larger Fabricators, |

|                | and 1        | 2" Wafers 4                              |

|                | 1.3 Litho    | graphy, Feature Size, and Cleaner        |

|                | Fabri        | cators and Equipment 4                   |

|                | 1.4 Defec    | et Density and the Need for Cleaner      |

|                | Fabri        | cators                                   |

|                | 1.5 Conc     | lusions7                                 |

| 2.0            | TECHNOL      | OGY TRENDS, CHIP SIZE,                   |

|                |              | ANCE, AND MOORE'S LAW7                   |

|                |              | rmance of Packaged Chips—Trends          |

| REF            | ERENCES .    |                                          |

| 1 |         | ition Technologies and Applications: Introduction verview |

|---|---------|-----------------------------------------------------------|

|   |         | r Kern and Klaus K. Schuegraf                             |

|   | 1.0     | OBJECTIVE AND SCOPE OF THIS BOOK 11                       |

|   | 2.0     | IMPORTANCE OF DEPOSITION                                  |

|   |         | TECHNOLOGY IN MODERN FABRICATION                          |

|   | 3.0     | PROCESSES                                                 |

|   | 5.0     | TECHNOLOGIES                                              |

|   | 4.0     | OVERVIEW OF VARIOUS THIN-FILM                             |

|   | т.0     | DEPOSITION TECHNOLOGIES                                   |

|   |         | 4.1 Evaporative Technologies                              |

|   |         | 4.2 Glow-Discharge Technologies 17                        |

|   |         | 4.3 Gas-Phase Chemical Processes                          |

|   |         | 4.4 Liquid-Phase Chemical Formation25                     |

|   | 5.0     | CRITERIA FOR THE SELECTION OF A                           |

|   |         | DEPOSITION TECHNOLOGY FOR SPECIFIC                        |

|   |         | APPLICATIONS                                              |

|   |         | <ul><li>5.1 Thin-Film Applications</li></ul>              |

|   |         | 5.2Matchai Characteristics305.3Process Technology32       |

|   |         | 5.4 Thin-Film Manufacturing Equipment                     |

|   | 6.0     | SUMMARY AND PERSPECTIVE FOR THE FUTURE. 36                |

|   | ACH     | XNOWLEDGMENTS                                             |

|   | REF     | TERENCES                                                  |

| 2 | Silicor | n Epitaxy by Chemical Vapor Deposition                    |

|   | Martin  | L. Hammond                                                |

|   | 1.0     | INTRODUCTION                                              |

|   | 1.0     | 1.1 Applications of Silicon Epitaxy                       |

|   | 2.0     | THEORY OF SILICON EPITAXY BY CVD 49                       |

|   | 3.0     | SILICON EPITAXY PROCESS CHEMISTRY                         |

|   | 5.0     | SILICON LI III MITTI I NOCLOD CILLWIDTICI                 |

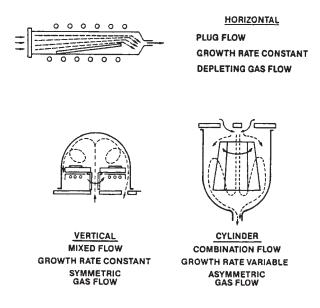

| 4.0  | COM  | IMERCIAL REACTOR GEOMETRIES      | 54  |

|------|------|----------------------------------|-----|

|      | 4.1  | Horizontal Reactor               | 55  |

|      | 4.2  | Cylinder Reactor                 | 56  |

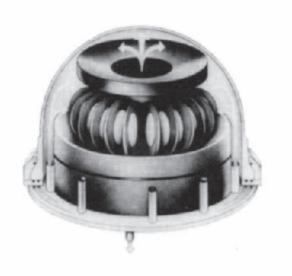

|      | 4.3  | Vertical Reactor                 | 56  |

|      | 4.4  | New Reactor Geometry             | 56  |

| 5.0  | THE  | ORY OF CHEMICAL VAPOR DEPOSITION | 57  |

| 6.0  | PRO  | CESS ADJUSTMENTS                 | 60  |

|      | 6.1  | Horizontal Reactor               | 61  |

|      | 6.2  | Cylinder Reactor                 | 63  |

|      | 6.3  | Vertical Reactor                 | 64  |

|      | 6.4  | Control of Variables             | 66  |

| 7.0  | EQU  | IPMENT CONSIDERATIONS FOR        |     |

|      | SILI | CON EPITAXY                      | 67  |

|      | 7.1  | Gas Control System               | 68  |

|      | 7.2  | Leak Testing                     | 68  |

|      | 7.3  | Gas Flow Control                 | 70  |

|      | 7.4  | Dopant Flow Control              | 72  |

| 8.0  | OTH  | ER EQUIPMENT CONSIDERATIONS      | 78  |

|      | 8.1  | Heating Power Supplies           |     |

|      | 8.2  | Effect of Pressure               | 78  |

|      | 8.3  | Temperature Measurement          | 79  |

|      | 8.4  | Backside Transfer                | 82  |

|      | 8.5  | Intrinsic Resistivity            | 83  |

|      | 8.6  | Phantom p-Type Layer             | 84  |

| 9.0  | DEF  | ECTS IN EPITAXY LAYERS           | 84  |

| 10.0 | SAFI | ETY                              | 87  |

| 11.0 | KEY  | TECHNICAL ISSUES                 | 87  |

|      | 11.1 | Productivity/Cost                | 87  |

|      | 11.2 | Uniformity/Quality               | 91  |

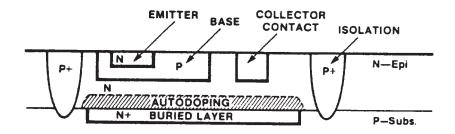

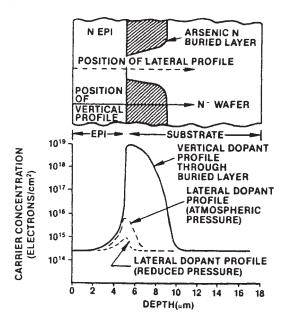

|      | 11.3 | Buried Layer Pattern Transfer    | 91  |

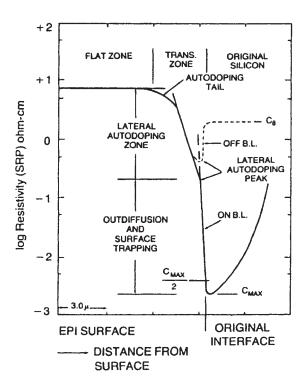

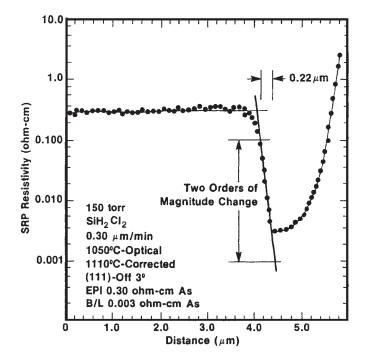

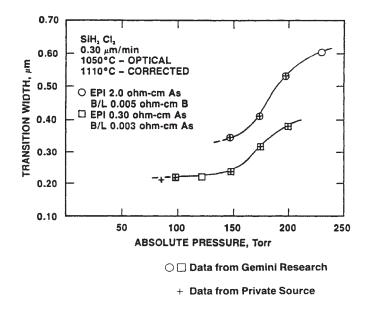

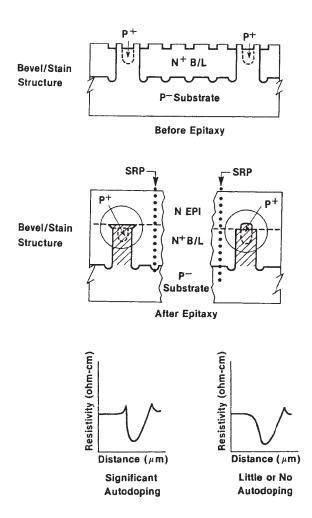

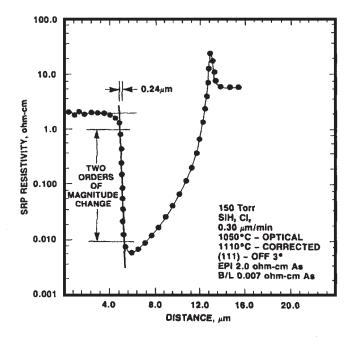

|      | 11.4 | Autodoping                       | 96  |

| 12.0 | NEW  | MATERIALS TECHNOLOGY FOR         |     |

|      |      | CON EPITAXY                      | 104 |

| 13.0 | LOW  | TEMPERATURE EPITAXY              | 105 |

|   | CO            | NCLUSIONS                                              |  |  |  |  |  |  |

|---|---------------|--------------------------------------------------------|--|--|--|--|--|--|

|   | REF           | FERENCES                                               |  |  |  |  |  |  |

| 3 | Chem          | ical Vapor Deposition of Silicon Dioxide Films 111     |  |  |  |  |  |  |

|   | John Foggiato |                                                        |  |  |  |  |  |  |

|   | 1.0           | INTRODUCTION                                           |  |  |  |  |  |  |

|   | 2.0           | OVERVIEW OF ATMOSPHERIC PRESSURE                       |  |  |  |  |  |  |

|   |               | CVD                                                    |  |  |  |  |  |  |

|   |               | 2.1 Basis of Atmospheric Deposition                    |  |  |  |  |  |  |

|   |               | 2.2 Parameters Affecting Chemical Reactions 120        |  |  |  |  |  |  |

|   |               | <ul> <li>2.3 Reaction Chamber Designs</li></ul>        |  |  |  |  |  |  |

|   | 2.0           |                                                        |  |  |  |  |  |  |

|   | 3.0           | PLASMA ENHANCED CHEMICAL VAPOR<br>DEPOSITION126        |  |  |  |  |  |  |

|   |               | 3.1 Deposition Rates                                   |  |  |  |  |  |  |

|   |               | 3.2 Film Characteristics for Different Chemistries 132 |  |  |  |  |  |  |

|   | 4.0           | PROPERTIES OF DIELECTRIC FILMS                         |  |  |  |  |  |  |

|   | 5.0           | NEW DEPOSITION TECHNOLOGIES                            |  |  |  |  |  |  |

|   |               | 5.1 Trends for CVD of Dielectric Films 143             |  |  |  |  |  |  |

|   | 6.0           | FUTURE DIRECTIONS FOR CVD OF                           |  |  |  |  |  |  |

|   |               | DIELECTRIC FILMS                                       |  |  |  |  |  |  |

|   | 7.0           | SUMMARY                                                |  |  |  |  |  |  |

|   | REF           | FERENCES                                               |  |  |  |  |  |  |

| 4 | Motol         | Organic Chemical Vapor Deposition: Technology          |  |  |  |  |  |  |

| - |               | quipment                                               |  |  |  |  |  |  |

|   |               | . Zilko                                                |  |  |  |  |  |  |

|   | 1.0           | INTRODUCTION                                           |  |  |  |  |  |  |

|   | 2.0           |                                                        |  |  |  |  |  |  |

|   | 3.0           | PHYSICAL AND CHEMICAL PROPERTIES                       |  |  |  |  |  |  |

|   | 5.0           | OF SOURCES USED IN MOCVD                               |  |  |  |  |  |  |

|   |               | 3.1 Physical and Chemical Properties of                |  |  |  |  |  |  |

|   |               | Organometallic Compounds                               |  |  |  |  |  |  |

|   |               | 3.2 Organometallic Source Packaging                    |  |  |  |  |  |  |

|   |               | 3.3 Hydride Sources and Packaging 171                  |  |  |  |  |  |  |

| 4.0                                      | GROWTH MECHANISMS, CONDITIONS,                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                          | AND CHEMISTRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 173                                                                                     |

|                                          | 4.1 Growth Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 173                                                                                     |

|                                          | 4.2 Growth Conditions, Chemistry and                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                          | Materials Purity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 174                                                                                     |

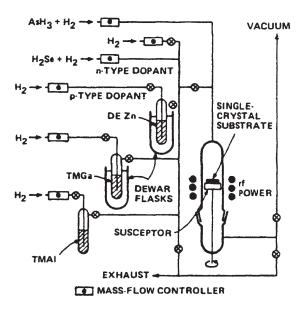

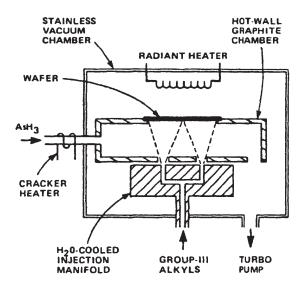

| 5.0                                      | SYSTEM DESIGN AND CONSTRUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 181                                                                                     |

|                                          | 5.1 Leak Integrity and Cleanliness                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 181                                                                                     |

|                                          | 5.2 Oxygen Gettering Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 182                                                                                     |

|                                          | 5.3 Gas Manifold Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 183                                                                                     |

|                                          | 5.4 Reaction Chamber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                          | 5.5 Exhaust and Low Pressure MOCVD                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 193                                                                                     |

| 6.0                                      | FUTURE DEVELOPMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 194                                                                                     |

|                                          | 6.1 Improved Uniformity Over Larger Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 195                                                                                     |

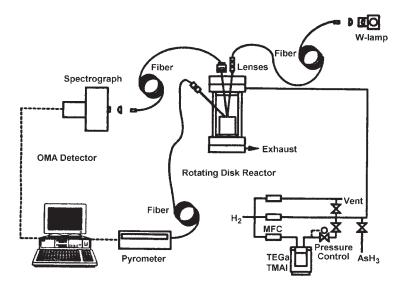

|                                          | 6.2 In-situ Diagnostics and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 195                                                                                     |

|                                          | 6.3 New Materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 199                                                                                     |

| $\Delta C$                               | KNOWLEDGMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 199                                                                                     |

| AC.                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|                                          | FERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 200                                                                                     |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 200                                                                                     |

| REI                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                         |

| REI<br>eatu                              | FERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

| REI<br>eatu                              | FERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 205                                                                                     |

| REI<br>eatu<br>ïvek                      | FERENCES<br>re Scale Modeling<br>Singh                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 205                                                                                     |

| REI<br><b>eatu</b><br><i>ïvek</i><br>1.0 | FERENCES<br><b>re Scale Modeling</b><br><i>Singh</i><br>INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b> 205</b>                                                                             |

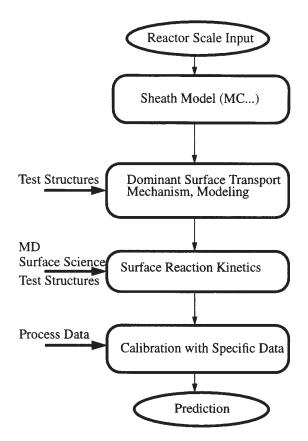

| REI<br>eatu<br>ivek<br>1.0               | FERENCES<br><b>re Scale Modeling</b><br><i>Singh</i><br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING                                                                                                                                                                                                                                                                                                                                                                                 | <b> 205</b><br>205<br>207                                                               |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING                                                                                                                                                                                                                                                                                                                                                                              | <b> 205</b><br>205<br>207<br>210                                                        |

| REI<br>eatu<br>ivek 1<br>1.0<br>2.0      | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath                                                                                                                                                                                                                                                                                                                                               | <b> 205</b><br>205<br>207<br>210<br>212                                                 |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath                                                                                                                                                                                                                                                                                                                                               | 205<br>205<br>207<br>210<br>212<br>213                                                  |

| REI<br>eatu<br><i>ivek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath<br>3.2 Selection of Surface Transport Mechanism<br>3.3 Surface Reaction Kinetics                                                                                                                                                                                                                                                              | 205<br>205<br>207<br>210<br>212<br>213<br>214                                           |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath<br>3.2 Selection of Surface Transport Mechanism<br>3.3 Surface Reaction Kinetics                                                                                                                                                                                                                                                              | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215                                    |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath<br>3.2 Selection of Surface Transport Mechanism<br>3.3 Surface Reaction Kinetics<br>3.4 Simplifying Assumptions                                                                                                                                                                                                                               | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215<br>216                             |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES<br>re Scale Modeling<br>Singh<br>INTRODUCTION<br>COMPONENTS OF ETCH AND DEPOSITION<br>MODELING<br>ETCH MODELING<br>3.1 Ion Transport in Sheath<br>3.2 Selection of Surface Transport Mechanism<br>3.3 Surface Reaction Kinetics<br>3.4 Simplifying Assumptions<br>3.5 Modeling of Surface Re-emission                                                                                                                                                                                        | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215<br>216<br>217                      |

| REI<br>eatu<br><i>ïvek</i><br>1.0<br>2.0 | FERENCES         re Scale Modeling         Singh         INTRODUCTION         COMPONENTS OF ETCH AND DEPOSITION         MODELING         3.1         Ion Transport in Sheath         3.2         Selection of Surface Transport Mechanism         3.3         Surface Reaction Kinetics         3.4         Simplifying Assumptions         3.5         Modeling of Surface Diffusion                                                                                                                 | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215<br>216<br>217<br>219               |

| REI<br>eatu<br>ivek<br>1.0<br>2.0<br>3.0 | FERENCES         re Scale Modeling         Singh         INTRODUCTION         COMPONENTS OF ETCH AND DEPOSITION         MODELING         ETCH MODELING         3.1       Ion Transport in Sheath         3.2       Selection of Surface Transport Mechanism         3.3       Surface Reaction Kinetics         3.4       Simplifying Assumptions         3.5       Modeling of Surface Re-emission         3.6       Modeling of Surface Diffusion         3.7       Numerical Methods               | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215<br>216<br>217<br>219<br>222        |

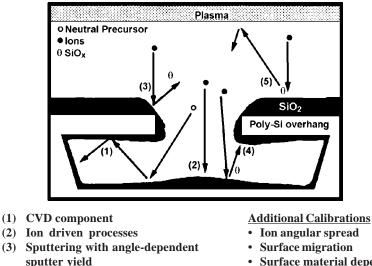

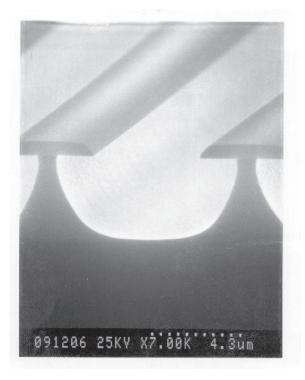

| REI<br><i>ivek</i><br>1.0<br>2.0<br>3.0  | FERENCES         re Scale Modeling         Singh         INTRODUCTION         COMPONENTS OF ETCH AND DEPOSITION         MODELING         3.1         Ion Transport in Sheath         3.2         Selection of Surface Transport Mechanism         3.3         Surface Reaction Kinetics         3.4         Simplifying Assumptions         3.5         Modeling of Surface Re-emission         3.6         Modeling of Surface Diffusion         3.7         Numerical Methods         ETCH EXAMPLES | 205<br>205<br>207<br>210<br>212<br>213<br>214<br>215<br>216<br>217<br>219<br>222<br>228 |

|   | 7.0    | REAL LIFE                                                                                                                                                                     |                                               |

|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   | REF    | FERENCES                                                                                                                                                                      |                                               |

| 6 | Semic  | ole Of Metrology And Inspection In<br>onductor Processing                                                                                                                     | 241                                           |

|   |        | Keefer, Rebecca Pinto, Cheri Dennison,<br>mes Turlo                                                                                                                           |                                               |

|   | 1.0    | OVERVIEW                                                                                                                                                                      | 241                                           |

|   | 2.0    | INTRODUCTION TO METROLOGY AND INSPECTION                                                                                                                                      | 242                                           |

|   | 3.0    | <ul> <li>METROLOGY AND INSPECTION TRENDS:</li> <li>PAST, PRESENT, AND FUTURE</li></ul>                                                                                        | 245<br>245<br>246                             |

|   | 4.0    | <ul> <li>THEORY OF OPERATION, EQUIPMENT DESI<br/>PRINCIPLES, MAIN APPLICATIONS,</li> <li>AND STRENGTHS AND LIMITATIONS OF</li> <li>METROLOGY AND INSPECTION SYSTEMS</li></ul> | IGN<br>255<br>256<br>261<br>264<br>269<br>277 |

|   | GLO    | OSSARY                                                                                                                                                                        |                                               |

|   | REF    | FERENCES                                                                                                                                                                      |                                               |

| 7 |        | mination Control, Defect Detection, and<br>Enhancement in Gigabit Manufacturing                                                                                               | 287                                           |

|   | Suresh | Bhat and Krishna Seshan                                                                                                                                                       |                                               |

|   | 1.0    | INTRODUCTION                                                                                                                                                                  |                                               |

|   | 2.0    | CONTAMINATION AND DEFECT GOALS<br>FOR ULSI DEVICES                                                                                                                            | 289                                           |

| SOURCES OF PARTICLES                         | 292                                                       |

|----------------------------------------------|-----------------------------------------------------------|

| CONTAMINATION AND DEFECT                     |                                                           |

| DETECTION: TOOLS OF THE TRADE                | 293                                                       |

| 4.1 Introduction                             | 293                                                       |

|                                              |                                                           |

|                                              |                                                           |

| 4.3 Patterned Wafer Surface Defect Detection | 297                                                       |

| ADVANCED TECHNIQUES FOR TRACE                |                                                           |

|                                              |                                                           |

|                                              | 299                                                       |

|                                              | 200                                                       |

|                                              |                                                           |

|                                              | 300                                                       |

|                                              | <b>2</b> 01                                               |

|                                              |                                                           |

|                                              |                                                           |

|                                              |                                                           |

| C C                                          |                                                           |

|                                              | 507                                                       |

|                                              | 307                                                       |

|                                              | 507                                                       |

| · · · ·                                      | 310                                                       |

|                                              |                                                           |

| EVOLUTION OF CIRCUIT BASED                   |                                                           |

| ELECTRICAL DEFECT DETECTION                  | 313                                                       |

| CONCLUSION                                   | 316                                                       |

| KNOWLEDGMENT                                 | 316                                                       |

| FERENCES                                     | 317                                                       |

|                                              |                                                           |

| ering and Sputter Deposition                 | . 319                                                     |

| n Rossnagel                                  |                                                           |

| INTRODUCTION                                 | 319                                                       |

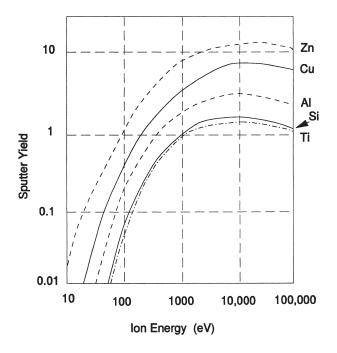

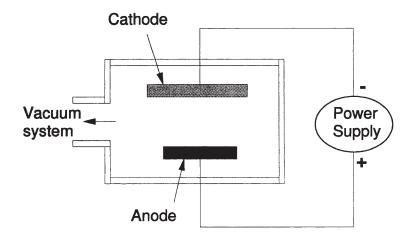

| PHYSICAL SPUTTERING THEORY                   | 320                                                       |

|                                              |                                                           |

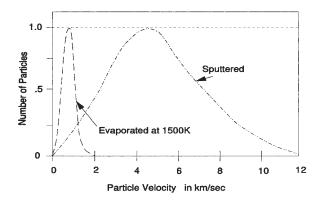

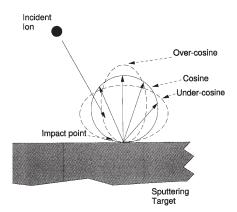

| 2.2 Energy and Direction of Sputtered Atoms  |                                                           |

|                                              | CONTAMINATION AND DEFECT<br>DETECTION: TOOLS OF THE TRADE |

| 3.0    | PLA        | SMAS AND SPUTTERING SYSTEMS                                                      | 326  |

|--------|------------|----------------------------------------------------------------------------------|------|

| 4.0    | DEP        | OSITION RATES AND EFFICIENCIES                                                   | 335  |

| 5.0    | REA        | CTIVE SPUTTER DEPOSITION                                                         | 338  |

| 6.0    | SPU        | TTERING SYSTEMS                                                                  | 344  |

| 7.0    | CON        | ICLUSIONS AND FUTURE DIRECTIONS .                                                | 347  |

| REF    | FERE       | NCES                                                                             | 348  |

|        |            |                                                                                  |      |

| Laser  | and ]      | Electron Beam Assisted Processing                                                | 349  |

| Camer  | on A.      | Moore, Zeng-qi Yu, Lance R. Thompson,                                            |      |

| and Ge | eorge.     | J. Collins                                                                       |      |

| 1.0    | INTI       | RODUCTION                                                                        | 349  |

| 2.0    | BEA        | M ASSISTED CVD OF THIN FILMS                                                     | 351  |

|        | 2.1        | Conventional CVD Methods                                                         |      |

|        | 2.2        | Electron Beam Assisted CVD                                                       |      |

|        | 2.3        | Laser Assisted CVD                                                               | 352  |

|        | 2.4        | Experimental Apparati of Beam                                                    |      |

|        |            | Assisted CVD                                                                     | 352  |

|        | 2.5        | Comparison of Beam Deposited Film                                                | 254  |

|        |            | Properties                                                                       |      |

| 3.0    |            | MICRON PATTERN DELINEATION WITH                                                  | ł    |

|        |            | GE AREA GLOW DISCHARGE PULSED                                                    | 0.65 |

|        |            | CTRON-BEAMS                                                                      |      |

| 4.0    |            | M INDUCED THERMAL PROCESSES                                                      |      |

|        | 4.1        | Overview                                                                         | 368  |

|        | 4.2        | Electron Beam Annealing of Ion-Implanted                                         | 270  |

|        | 4.3        | Silicon                                                                          |      |

|        | 4.5<br>4.4 | Electron Beam Alloying of Silicides<br>Laser and Electron Beam Recrystallization |      |

|        | 4.4        | of Silicon on $SiO_2$                                                            | 374  |

| 5.0    | SUM        | IMARY AND CONCLUSIONS                                                            |      |

| 0.0    |            | VLEDGEMENTS                                                                      |      |

|        |            |                                                                                  |      |

| KEF    | EKE        | NCES                                                                             |      |

| 10 |     | cular Beam Epitaxy:<br>oment and Practice                                                    | 201 |

|----|-----|----------------------------------------------------------------------------------------------|-----|

|    |     | S. Knodle and Robert Chow                                                                    | 301 |

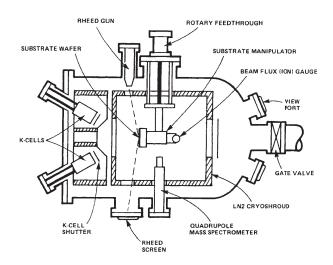

|    | 1.0 | THE BASIC MBE PROCESS                                                                        | 382 |

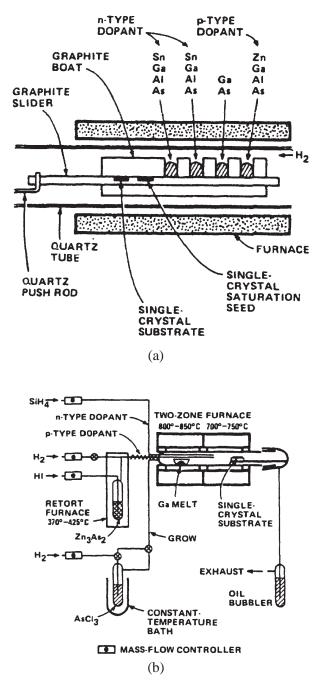

|    | 2.0 | COMPETING DEPOSITION TECHNOLOGIES                                                            | 385 |

|    |     | 2.1 Liquid Phase Epitaxy                                                                     |     |

|    |     | 2.2 Vapor Phase Epitaxy and MOCVD                                                            |     |

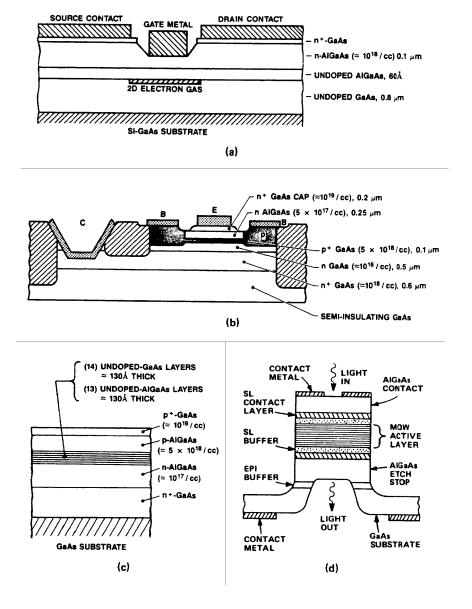

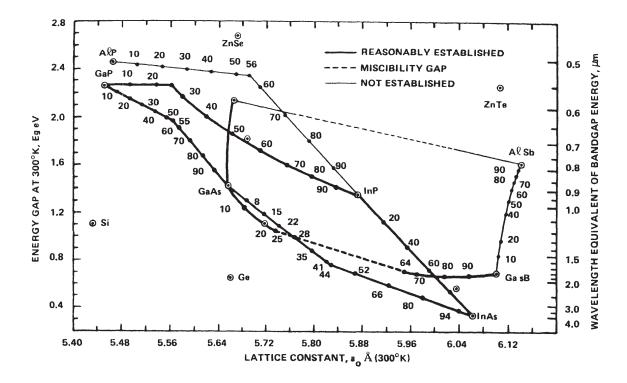

|    | 3.0 | MBE-GROWN DEVICES                                                                            | 390 |

|    |     | 3.1 Transistors                                                                              |     |

|    |     | 3.2 Microwave and Millimeter Wave Devices                                                    | 396 |

|    |     | 3.3 Optoelectronic Devices                                                                   | 396 |

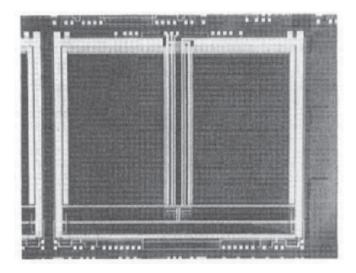

|    |     | 3.4 Integrated Circuits                                                                      | 397 |

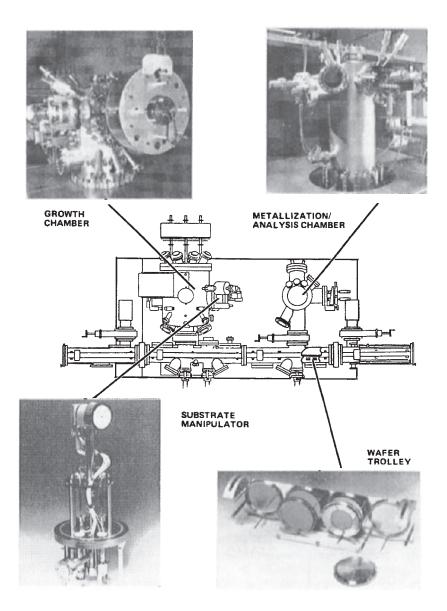

|    | 4.0 | MBE DEPOSITION EQUIPMENT                                                                     | 398 |

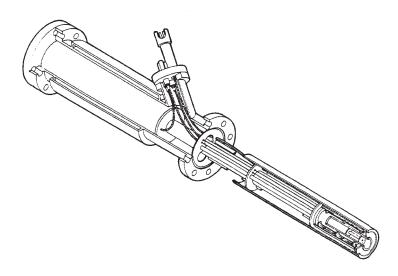

|    |     | 4.1 Vacuum System Construction                                                               | 399 |

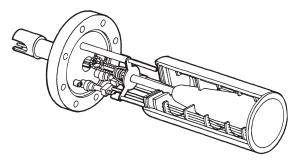

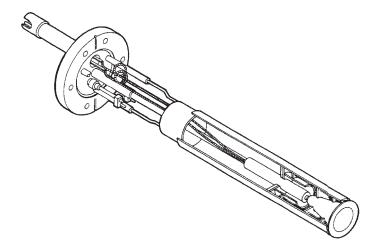

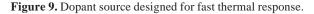

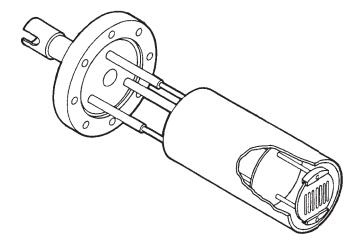

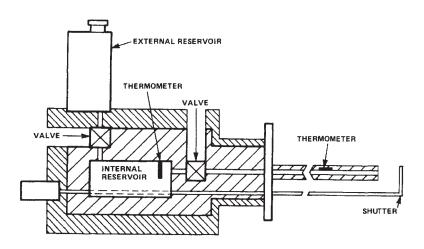

|    |     | 4.2 Sources                                                                                  | 403 |

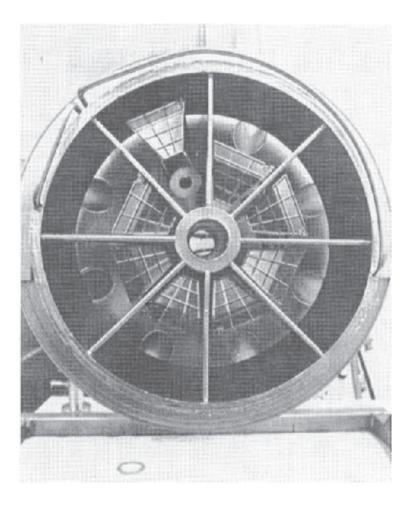

|    |     | 4.3 Sample Manipulation                                                                      |     |

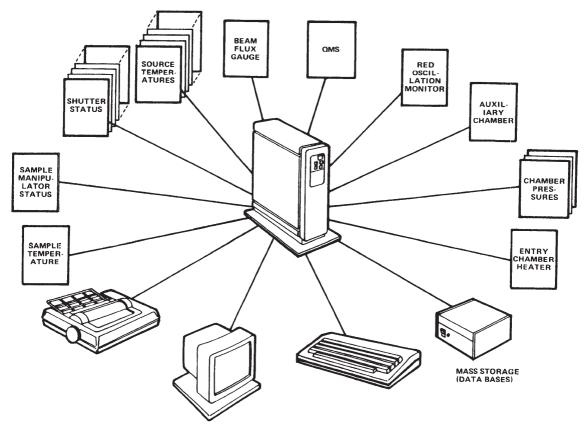

|    |     | 4.4 System Automation                                                                        |     |

|    |     | 4.5 Performance Parameters                                                                   | 412 |

|    | 5.0 | PRINCIPLES OF OPERATION                                                                      |     |

|    |     | 5.1 Substrate Preparation                                                                    |     |

|    |     | 5.2 Growth Procedure                                                                         |     |

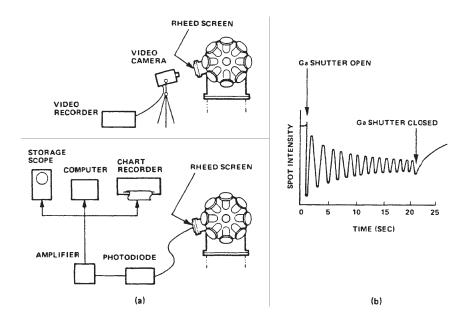

|    |     | 5.3 In Situ Analysis                                                                         |     |

|    |     | 5.4 Materials Evaluation                                                                     |     |

|    |     | 5.5 Safety                                                                                   |     |

|    | 6.0 | RECENT ADVANCES                                                                              |     |

|    |     | 6.1 RHEED Oscillation Control                                                                |     |

|    |     | 6.2 GaAs on Silicon                                                                          |     |

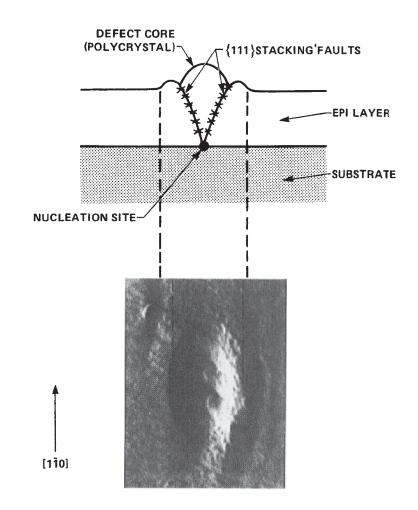

|    |     | <ul><li>6.3 Oval Defect Reduction</li><li>6.4 Chemical Beam Epitaxy/Gas Source MBE</li></ul> |     |

|    |     | 6.5 Superlattice Structures                                                                  |     |

|    | 7.0 | -                                                                                            |     |

|    | 7.0 | FUTURE DEVELOPMENTS<br>7.1 Production Equipment                                              |     |

|    |     | <ul><li>7.1 Production Equipment</li><li>7.2 In Situ Processing</li></ul>                    |     |

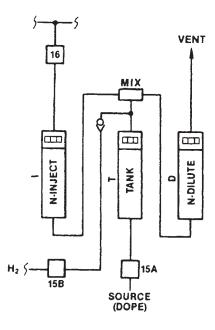

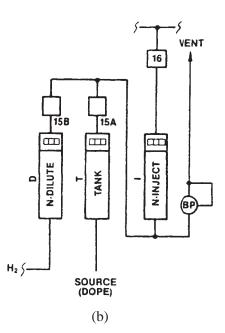

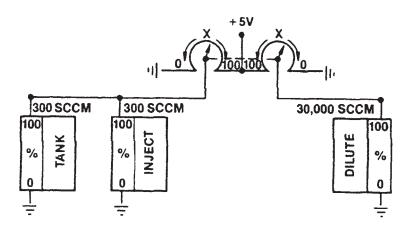

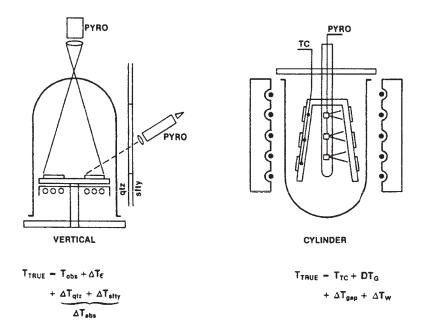

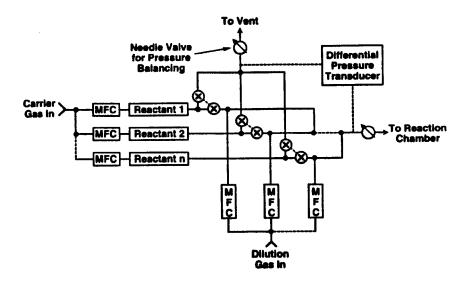

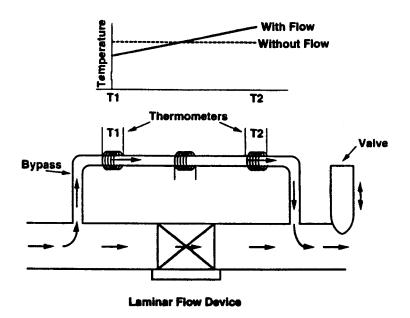

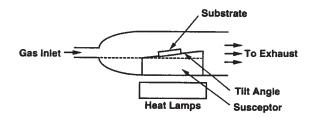

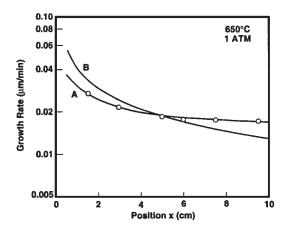

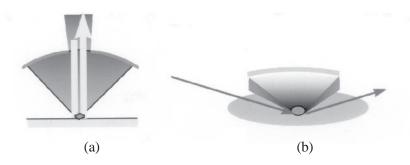

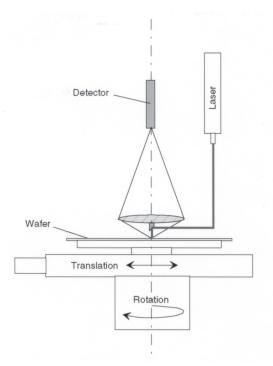

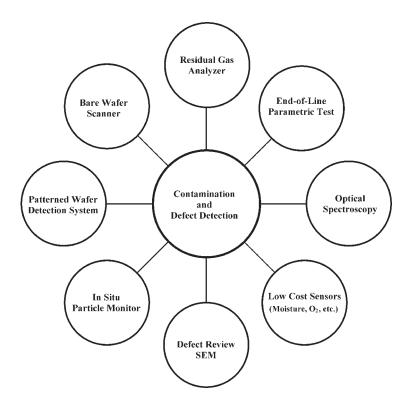

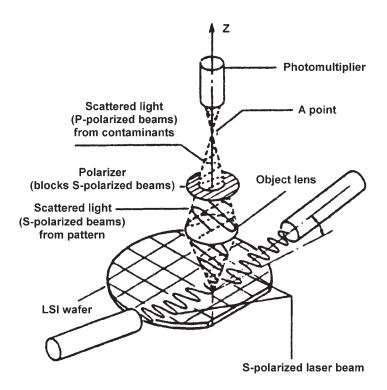

|    |     | <ul><li>7.2 In Stu Processing</li><li>7.3 Process Developments</li></ul>                     |     |